When

Where

Färögatan 33, Kista

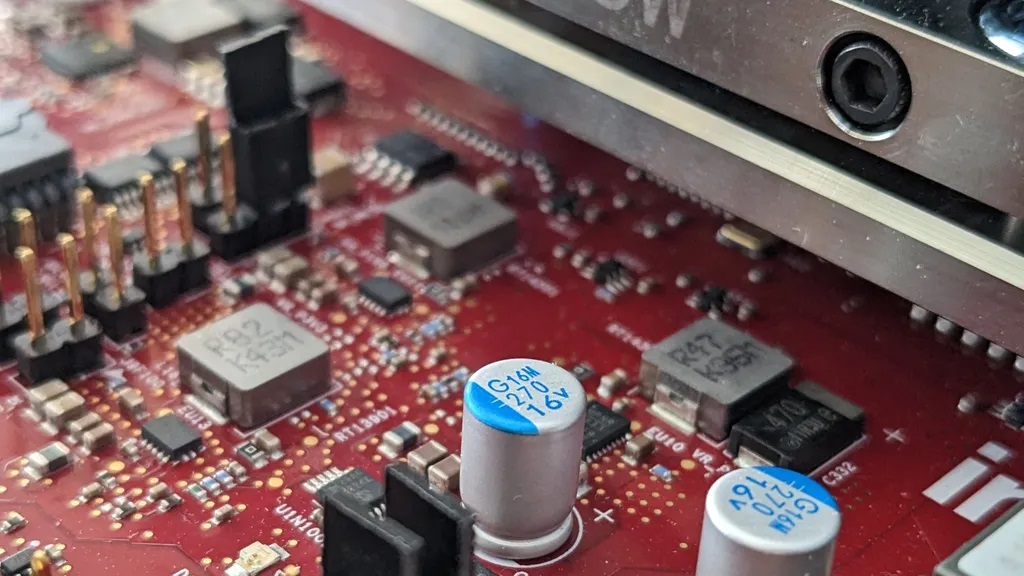

Packet networks is not socket science. Time, power, and synchronization and the lower layers.

Join our new meetup series “Computer and Systems Architecture meetup”, for us working in the field of computer and system architecture.

Agenda

17:00 Doors open

17:15 Welcome

17:30 Presentation “Network Time and Frequency Synchronization”, by Hans Brandberg

18:00 Presentation 2, by Per Holmberg

18:30 Networking, food and drinks (at own expence)

19:00 Joint Q&A

21:00 Event closes

Meet the speakers

Hans Brandberg is a Network Systems and Solutions Engineer at Intel. Before joining Intel earlier this year, he has been working with products and solutions for time and frequency synchronization for the last 15 years at various companies.

Per Holmberg is a Computer Architect that worked at Ericsson in several specialist and expert positions related to computer and processor architecture and design. Experience includes design of high performance and high availability embedded processing and communication systems, custom processors, offload and I/O accelerators and ASICs design. Current interests include RISC-V, low latency communication and energy efficiency.

Abstracts

Time and Frequency Synchronization – What time is it and how can we tell others about it? Most modern communication is based on packet transport, a method which basically has no idea about time. Still the end applications using it puts higher and higher demand on time and frequency synchronization. What are the challenges in distributing accurate time and how can this be solved? This presentation will give some history on time distribution, talk about the current methods and standards of distributing time and give examples of what accuracy that can be achieved.

Presentation 2 – Energy efficiency is now a top priority, but power management in high speed networking systems is very challenging. Rapid and unpredictable changes in the packet traffic can cause disturbances such as packet drops, added delays or jitter in the packet stream. For these applications, processor power management is often used in a limited way for selected low traffic use-cases or completely turned off.

The presentation describes a promising new method for high speed networking: applying micro-sleeps for high performance packet processing. Micro-sleeps can be opportunistically applied in all idle periods, thereby saving energy across a wide range of traffic conditions. The presentation describes architectural considerations for achieving best energy efficiency, HW and SW support now available (e.g. x86 processors and DPDK framework), and the HW and SW integration into the packet processor infrastructure. Results are encouraging showing very good power saving in full application tests and stress tests show that no disturbances are caused in high-speed packet streams.